# ASEAN Engineering Journal

## PACKAGE-ON-PACKAGE (POP) UNDERFILL PROCESS USING A MATERIAL DAM METHOD

Mohd Yusuf Tura Ali<sup>a, b</sup>, Chu Yee Khor<sup>b\*</sup>, Azwan Iskandar Azmi<sup>b</sup>, Mohd Zulklifly Abdullah<sup>c</sup>, Zambri Samsudin<sup>a</sup>, Idris Mansor<sup>a</sup>, Muhammad Irsyad Suhaimi<sup>a</sup>, Muhammad Syahir Mahyuddin<sup>a,c</sup>, Lai Ming Lim<sup>a</sup>

<sup>a</sup>Jabil Circuit Sdn. Bhd. 56, Hilir Sungai Keluang 1, Bayan Lepas Industrial Park, Phase 4, 11900 Penang, Malaysia.

<sup>b</sup>Faculty of Mechanical Engineering Technology, Universiti Malaysia Perlis (UniMAP), Perlis, Malaysia.

<sup>c</sup>School of Mechanical Engineering, Engineering Campus, Universiti Sains Malaysia, Nibong Tebal, 14300, Penang, Malaysia.

#### Article history

Full Paper

Received 19 July 2021 Received in revised form 17 September 2021 Accepted 01 December 2022 Published online 31 May 2022

\*Corresponding author cykhor@unimap.edu.my

#### Graphical abstract

#### Abstract

Recent developments in the electronics industry have introduced a multi-stack ball grid array (BGA) to meet the growing consumer demand for both high-performance and smaller-sized chip packages. This study focused on the preliminary study of the Package-on-Package (PoP) underfill process using a material dam method. High viscosity type of underfill material is considered for the underfill process. In the current experimental work, L path-dispensing method was chosen due to its advantages, as reported in the previous work. The material dam method was used to prevent underfill from moving backwards and flowing out from the dispensing region. The material dam was built surrounding the PoP package. The effectiveness of the underfill process was analyzed based on the cycle time and lateral lapping, which are significant factors in material selection. The experimental results revealed that slow underfill flow may cause the quickly harden of material while the dispensing process is still running. This situation restricts the underfill flow and creates voids in the PoP package. The material dam method successfully enhanced the underfilling process for layers 3 and 4 stacked-package. This study is expected to provide the preliminary underfill process of stacking the PoP package and is useful as a reference for the engineer in the microelectronics industry.

Keywords: Package-on-Package, Underfill Process, L path-dispensing method, Material dam method, ball grid array.

© 2022 Penerbit UTM Press. All rights reserved

### **1.0 INTRODUCTION**

Today, microelectronic technology proliferates from a single integrated circuit (IC) package to compact and multi-stacked IC packages. The growth of this technology is highly beneficial to our life. In microelectronic technology, one crucial area is the design and assembly of the integrated circuit (IC). Package-on-Package (PoP) is a recent IC packaging technology that applies to various applications due to its compact characteristics compared to the standard single IC package. Package-on-Package (PoP) is the primary approach for 3D Packaging. The process is shown by vertically combining the discrete memory and the logic ball grid array (BGA) packages, where the package rests on top of each other. Recently, Package-on-package technologies have attracted lots of attention, especially for the use of portable electronics related to products and applications [1]. PoP stacks in manufacturing or improvement consist of a bottom package containing a high-performance machine designed to combine the top package where it usually contains a high-load or the combination memory devices. The rapid growth of portable equipment has led to intense demands for further miniaturization, lightening, and higher performance, especially in the arena of cellular phones, PDAs and digital cameras. This situation shows that the package stacking operation is an important technology that gives the system manufacturer the option of choosing the top and bottom of the component from different suppliers. Each package has different types of warpage trends from room temperature to reflow temperature [2]. Due to enhancing the PoP's reliability, the underfill is applied to fill the intermediate gap between the stacked chips.

The underfill process is broadly used in electronic construction to increase its strength. The current fluxing process is applied by distributing the chosen volume onto the circuit board with an optimized pattern. The underfill cure is done simultaneously with the arrangement of a solder joint in the process of reflow. Though the time for dispensing to process the underfill material for automated underfill with the jetting head is much faster than the conventional capillary underfill process. The time taken for processing the underfill dispensing will take much slower than any other of the process steps (e.g. chip placement, reflow, printing, etc.). This condition means that the underfill dispensing will cause congestion in the high-speed electronic assembly process. Apart from the slow processing time, this underfills the dispensing process needs a complex and expensive machine that will add more cost to the manufacturer [3]. The underfill process is inserted near the edge of a flip chip or CSP to apply the capillary force to enclose the gap between the component and board. The distribution of the capillary underfill material requires special equipment to achieve the accuracy and precision necessary for a mass assembly. At the most, the dispenser must repeatedly apply a consistent assembly and apply a preset volume of underfill toward the edge of the component [4].

The introduction of a multi-stack ball grid array (BGA) to improve the performance of the conventional BGA flip chip encountered several issues, including extended filling time and incomplete filling at the multi-stack BGA's upper layer. Due to the lower hydrostatic pressure in the upper layer, it was discovered that the underfill encapsulant lacks the energy necessary to flow at that layer [5]. This situation added thermal energy in the upper layer results in a distinct temperature difference between the upper and lower layers referred to as a thermal delta. Through experimentation and numerical simulations, this research sought to demonstrate the efficacy of thermal delta in resolving the low mentioned above during the encapsulation of a multi-stack BGA [6]. The ball grid array has been the subject of significant research (BGA). Khor et al. (2012) [7] standardized the array architecture to find a better encapsulation process, thereby minimizing stress and deformity of the whole integrated circuit (IC) structure. They eventually optimized the perimeters of a  $10 \times 10$  solder bump array in terms of standoff height, chip thickness, and the gap at a particular inlet pressure. This research was crucial in designing the best IC package that can work well with the encapsulation process to strengthen the IC package. Another study on the BGA encapsulation process was conducted by Abas et al. (2016) [8]. They used both the lattice Boltzmann method (LBM) and finite volume method (FVM) to simulate the flow of a simple 6×6 BGA in the encapsulation process. The group showed a good agreement about filling time for both LBM and FVM simulations. Apart from that, Abas et al. (2016) [9] also studied the encapsulation of BGA with various types of arrangement, such as its perimeters, full and middle empty orientations. LBM's simulations and experiment determined the fluid's pace and pressure distribution for each case. The BGA was discovered to have the fastest underfilling flow with a

perimeter orientation followed by the BGA's full orientation and middle empty.

The incomplete filling or voiding is the main problem in the underfill process [10]. The void in the package could induce unintended problems such as the pop-corn phenomenon and solder extrusion [11] during the reflow soldering process. Many attempts have been made to minimize and eliminate the void defects. Vacuum moulded underfill was applied to the flip-chip package underfill process [12]. The simulation model predicts the void size and its characteristics via computational fluid dynamics [11 & 12] in the Flip-chip PoP. A multi-zone porous media model was considered for the complex ball grid array in the simulation. Moreover, the PoP technology is also applied at the wafer level [13]. Fan-out wafer-level PoP was cost-effective compared to the flip-chip PoP for the small package size. However, the flip-chip PoP is cost-effective when using the large package size in the handling process. Due to the greater die size, the typical flip chip POP structure has difficulty supporting high bandwidth top memory I/O counts in a tiny package [14]. An Interposer substrate with copper (Cu) could overcome the fine pitch problem and improve the package warpage/coplanarity and reliability. Besides, the interposer application also enhances interconnect, and solder join defects such as non-wets and bridges [15].

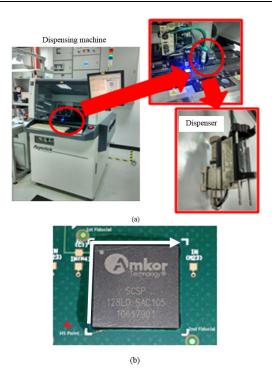

This study conducted the experimental analysis of the Package-on-Package (PoP) underfill process in Jabil Circuit Sdn. Bhd. Penang, Malaysia. An automated dispensing machine with the jetting head was employed to dispense the underfill materials on 3- and 4-stacked PoP, as shown in Figure 1. The L-dispensing method was considered during underfill process. The underfill filling time and voids of the package were studied in the underfill experiments. Besides, the current research also visualized the underfill flow at each layer of the PoP by the lateral lapping cross-section method. It also aimed to enhance the productivity of the underfill process with the shortest possible filling time and minor reliability issues (e.g., voids and incomplete filling).

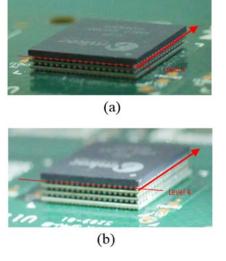

Figure 1 (a) 3 PoP stacks and (b) 4-stack PoP with lateral lapping direction for the void analysis

#### 2.0 METHODOLOGY

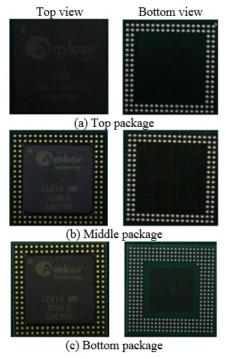

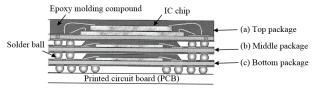

Amkor PoP was used in the experimental study. Figure 2 shows the PoP package for different layers of the chip package. The bottom package is attached to the PCB/substrate and subsequently followed by the middle and top packages in the vertical direction. The interconnection of the PoP is connected via the solder ball (as illustrated in the bottom view) and the copper ball pad (on the middle and bottom packages). The intermediate space between the packages is to be filled by the encapsulation material via the underfill process in the electronic assembly line.

Amkor's printed circuit board (PCB) and PoP were considered for the current experimental study. This type of PoP package is newly introduced for high-performance portable electronic devices. The PCB dimensions are 132 mm × 77 mm, and the size of PoP is 12 mm × 12 mm. The PoP package for each layer (i.e., top, middle and bottom) has different numbers of input/output (I/O) as designed by the Amkor manufacturer, according to the application of PoP in electronic devices. The assembled PoP package will undergo the 'L' type of underfill process in the current experiment. The structure of the assembled PoP package is depicted in Figure 3. The underfill material will fill up the intermediate space between the PoP packages during the underfill process, providing better strength to the entire stack's PoP.

Figure 2 Top view and bottom view of the PoP actual packages before underfill process

Figure 3 Illustration of Package-on-Package structure (Source: www.amkor.com)

Table 1 summarizes the details of the underfill dispensing machine and the underfill material for the experimental study. Asymtek X-1020 dispensing machine with the jetting head type (Figure 4a) is employed to conduct the PoP underfill process in Jabil Circuit Sdn. Bhd. in Penang, Malaysia. The underfill material (Brand A) is considered for the underfill process. Generally, underfill process can be performed using different dispensing methods such as I, U and L. The current study selected the L-path dispensing method (Figure 4b) due to its advantages. L-path yields less voiding and a better filling process, as reported previously.

| Table 1 Machine | and set | t up for | underfill | process |

|-----------------|---------|----------|-----------|---------|

|-----------------|---------|----------|-----------|---------|

| Category   | Specifications                                    | Details                                                       |  |

|------------|---------------------------------------------------|---------------------------------------------------------------|--|

| Machine    | Machine Model:<br>Valve Configuration:<br>Nozzle: | Asymtek X-1020<br>Dispensing Jetting head<br>Ø0.125mm (outer) |  |

|            | Reworkable:                                       | Yes                                                           |  |

|            | Pre-heat :                                        | Yes (PCB & material)                                          |  |

| Materials  | Density (g/cm <sup>3</sup> ):                     | 1.3                                                           |  |

|            | Viscosity:                                        | 10,000 cps (10 Pa.s)                                          |  |

|            | T <sub>g</sub> (°C):                              | 105                                                           |  |

| Dispensing | Pattern:                                          | L-path                                                        |  |

Figure 4 (a) Underfill dispenser machine and configuration and (b) Lpath underfill dispensing pattern

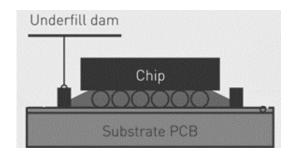

The underfill process of PoP is challenging because the stacked package's presence has increased the overall thickness of the package. It means that the PoP is thicker than a single flip chip. Without any underfill dam, the underfill could not fill the intermediate space of the 3 and 4 stacks of PoP. This situation also indicates that 0% of underfill material is in that space. Therefore, to ensure the underfill material can be filled to the top layer of the PoP package, the proposed method is

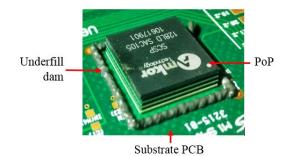

using underfill dam, as depicted in Figure 5. In the experiment, the underfill dam (Figure 6) is created surrounding the package. The underfill dam was created using the high viscosity (63 Pa.s) underfill material via the dispensing machine. Underfill material is dispensed according to the L-path dispensing pattern. The function of underfill dam is to hold the material from flowing out instead of increasing the material level in the dam. When the material increases, it will seep into the packages up to the highest level. After completing the underfill process, the underfilled package with underfill dam will be cured in the curing process.

Figure 5 Dispense underfill dam for building a wall (Sources: www.spts.com)

Figure 6 Underfill dam surrounding the PoP in the current experiment

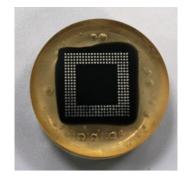

After the underfill material was cured, the destructive analysis technique was applied to conduct a lateral crosssection analysis on the PoP packages. Figure 7 shows the sample of the lateral lapping of the PoP package. The crosssection of the PoP packages allows the inspection of the defects, such as voids under the package. The sample was mounted on a specially designed moving table that oscillated in the X and Y directions. The z-axis-controlled rotating tool ensured a precise grinding down to a specified thickness.

Figure 7 Lateral lapping of the PoP package after the underfill process

#### **3.0 RESULTS AND DISCUSSION**

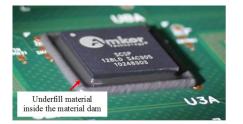

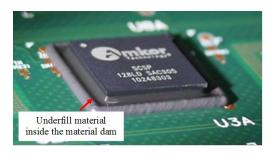

The underfill experiments of the PoP were carried out according to the methodology aforementioned. Figure 8 shows the underfill material filled the underfill dam after the dispensing step from the jetting head in the current experiment. The underfill material flows into the intermediate scape between the packages via the capillary action of a tiny gap. From the observation, there is no overflow of the underfill material from the dam. The presence of underfill dam has facilitated the filling process of the space beneath the top package. The proper processes for applying capillary and noflow underfill are more critical today than ever before because it allows the continued growth and application of flip chips [16]. In any underfill application, it is first necessary to analyze the system's integrity to determine the required dispensing parameters. The volume of underfill material dispensing equals the amount of the fluid below the die (average space between the die and substrate). It deducts the volume of the solder bumps and the fillet volume around the silicon die. When the minimal volume of the underfill material occurs, the bumps will be at their highest. The filler width and height are at a minimum, and the die size is maximum. For example, the silicon die has insufficient underfill, and the fillet height has a minimal amount of fluid during the dispensing of underfill process. However, the maximum amount of underfill is allowed when the fillet width and height are maximum, and the smallest die size.

By using the tools for defining underfilling volumes and fillet sizes [17], underfilling has become a robust manufacturing process. Process engineers can use transparent dies [18,19], and different coloured underfills if a flow analysis is required. The industry used the 'l' and 'L' path techniques [20], followed by a seal pass. The underfill process was brought with a new level of robustness when jetting technology was introduced. The problem areas due to needles will become obsolete by eliminating the needle from the dispensing process. Thus, jetting technology is shown to increase the throughput and yield of the underfill process. Currently, jetting technology can be used on many materials. Hardened parts solve the wear and tear problem from concurrent usage for the underfill material. The low cost of ownership as most fluids are used with the mechanical jet. Even the low range of 500 cps can be used at high jet velocities without splashing. The range of the jet is robust.

Figure 8 Underfill Material - Underfill inside the material dam

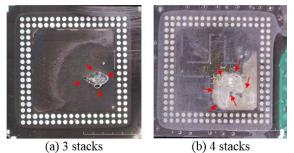

The experimental results show that the underfill material with 10000 cps of viscosity was successfully dispensed on 3 stacks package. From the observation during the experiment, the underfill material filled the intermediate space of the PoP. Lateral lapping results show that the underfill materials are able to seep under the package (Figure 9a). The underfill material covered nearly 90% of the intermediate space, which meets the requirement of the underfill process. The 3 stacks experimental results show that this experiment was successful, and the experiment was extended using 4 stacks PoP package. Similarly, the underfill by using the material dam method was also successful for the 4 stacks PoP package. Figure 9b shows the underfill material successfully seeps under the package and fills the intermediate space between the stacking packages.

Figure 9 Lateral lapping results of (a) 3 stacks and (b) 4 stacks

The main factor in dispensing a high viscosity material is preheated with a specific temperature. The board must preheat at a certain temperature. The underfill material must be preheated before it can be dispensed onto the board. The material will melt and easily flow into the intermediate space between the packages by applying heat correctly. However, extra time is required for the preheat temperature to reach the specified level before the machine dispenses the underfill material. Table 2 summarizes the cycle time of the underfill process for each layer of PoP. The underfill material can be controlled entirely inside the dam without flowing out using the material dam method. This method enhances the underfill process for the stacking chip package.

No of Package Dispensing time Total dispensing time (sec) stacks Layer (sec) 3 stacks Bottom 55 2<sup>nd</sup> 65 155 3<sup>rd</sup> 35 4 stacks 4<sup>th</sup> 50 205

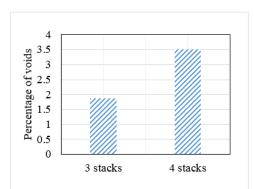

The percentage of voids was measured using the Hirox scope. As shown in Figure 9, the void area was measured and calculated over the package size (160 mm<sup>2</sup>). From the experimental results, the percentages of voids for three stacks and four stacks are 1.88% and 3.52%, respectively (Figure 10). These results also indicated that the underfill material filled the intermediate space up to 90%, which fulfilled the requirements of the underfill process.

Figure 10 Percentage of void for 3 stacks and 4 stacks chip after the underfill process

#### 4.0 CONCLUSION

The experiments of the underfill process on the PoP package were successfully conducted using the dispensing machine in Jabil Circuit Sdn. Bhd.. The material dam was built surrounding the PoP package to prevent the backward flow of the underfill material during the process. L path-dispensing method was applied to the dispensing pattern. The experimental results showed that the underfill material successfully filled the intermediate space of the PoP package, and almost 90% of filling was observed at layers 3 and 4. This finding indicated that the material dam method enhances the filling of underfill into the intermediate space of layers 3 and 4. This study will be extended to the parametric investigation of different underfill process parameters, such as the influence of underfill viscosity, dispensing type, and dispensing speed.

#### Acknowledgement

The authors fully acknowledged Jabil Circuit Sdn. Bhd. for the technical support which makes this vital research viable and effective.

Table 2 Cycle time by package layer using material dam method

#### References

- Vianco, P. and Neilsen, M., 2021. Processing and Reliability of Solder [1] Interconnections in Stacked Packaging. In 3D Microelectronic Packaging, 471-526. https://doi.org/10.1007/978-981-15-7090-2\_16

- Yoshida, A., Taniguchi, J., Murata, K., Kada, M., Yamamoto, Y., Takagi, Y., Notomi, T. and Fujita, A., 2006, May. A study on package stacking process for package-on-package (PoP). In 56th *Electronic* [2] Components and Technology Conference 2006, 6.

- Zhang, J. and Baldwin, D.F., 2003, May. High-speed SMT compatible [3] dispenseless underfill process for CSP BGA flip chip assembly. In 53rd Electronic Components and Technology Conference, 2003 Proceedings. 870-874.

- Toleno, B.J. and Schneider, J., 2003, July. Processing and reliability of corner bonded CSPs. In IEEE/CPMT/SEMI 28th International [4] Electronics Manufacturing Technology Symposium, 2003. IEMT 2003. 299-304.

- Ng, F.C., Abas, A., Ishak, M.H.H., Abdullah, M.Z. and Aziz, A., 2016. [5] Effect of thermocapillary action in the underfill encapsulation of multi-stack ball grid array. *Microelectronics Reliability*, 66: 143-160. https://doi.org/10.1016/j.microrel.2016.10.001

- Ong, E.E., Abdullah, M.Z., Khor, C.Y., Loh, W.K., Ooi, C.K. and Chan, R., [6] 2012. Analysis of encapsulation process in 3D stacked chips with different microbump array. International Communications In Heat And Mass Transfer, 39(10): https://doi.org/10.1016/j.icheatmasstransfer.2012.10.007 1616-1623.

- Khor, C.Y., Abdullah, M.Z., Tan, H.T., Leong, W.C. and Ramdan, D., [7] 2012. Investigation of the fluid/structure interaction phenomenon in IC packaging. Microelectronics Reliability, 52(1): 241-252. https://doi.org/10.1016/j.microrel.2011.09.013 Abas, A., Ishak, M.H.H., Abdullah, M.Z., Ani, F.C. and Khor, S.F., 2016. Lattice Boltzmann method study of bga bump arrangements on void

- [8] formation. *Microelectronics Reliability,* https://doi.org/10.1016/j.microrel.2015.10.014 Reliability, 170-181. 56:

- Abas, A., Haslinda, M.S., Ishak, M.H.H., Nurfatin, A.S., Abdullah, M.Z. [9] and Ani, F.C., 2016. Effect of ILU dispensing types for different solder bump arrangements on CUF encapsulation process. *Microelectronic Engineering*, 163: 83-97. https://doi.org/10.1016/j.mee.2016.06.010 Khor, C.Y., Abdullah, M.Z., Lau, C.S. and Azid, I.A., 2014. Recent fluid-

- [10] structure interaction modeling challenges in IC encapsulation-A Reliability, review Microelectronics 54(8): 1511-1526. https://doi.org/10.1016/j.microrel.2014.03.012

- Lee, M.S., Baick, I.H., Lee, M., Kim, B., Lee, M., Kang, H., Kim, J., Rhee, H. and Pae, S., 2019, October. PCB Strip Scale Numerical Study on [11]

Vacuum Molded Underfill Void Entrapment in FC-POP Devices. In 2019 IEEE International Integrated Reliability Workshop (IIRW), 1-5. https://doi.org/10.1109/IIRW47491.2019.8989917

- Lee, M.S., Baick, I., Jeong, M.S., Kim, M., Kwon, S.H., Yeo, M.S., Rhee, H. and Pae, S., 2020. Parametric Study on the Void Risk in FC-POP [12] Molded Underfill Process Using a Novel Porous Media, Two-Phase, Compressible Flow Simulation Method. IEEE Transactions on Device and Materials Reliability, 292.https://doi.org/10.1109/TDMR.2020.2985209 20(2): 286-

- Lujan, A.P., 2018, May. Comparison of Package-on-Package Technologies Utilizing Flip Chip and Fan-Out Wafer Level Packaging. [13] In 2018 IEEE 68th Electronic Components and Technology Conference (ECTC), 2089-2094. https://doi.org/10.1109/ECTC.2018.00313

- Hsieh, M.C., Lin, S., Hsu, I., Chen, C.Y. and Cho, N., 2017, September. Fine pitch high bandwidth flip chip package-on-package development. In 2017 21st European Microelectronics and Packaging [14] Conference (EMPC) & E https://doi.org/10.23919/EMPC.2017.8346847 Exhibition,

- Gagnon, P., Fortin, C. and Weiss, T., 2019, May. Package-on-Package micro-BGA Microstructure Interaction With Bond and Assembly Parameter. In 2019 IEEE 69th Electronic Components and Technology [15] Conference (ECTC). 306-313). https://doi.org/10.1109/ECTC.2019.00053

- https://doi.org/10.1109/ECIC.2019.00053 Gwon, H.R., Lee, H.J., Kim, J.M., Shin, Y.E. and Lee, S.H., 2014. Dynamic behavior of capillary-driven encapsulation flow characteristics for different injection types in flip chip packaging. *Journal of Mechanical Science and Technology*, 28(1): 167-173. https://doi.org/10.1007/s12206-013-0950-9 Babiarz, A.J., Paradigm Shift in Applying Underfill. Asymtek, Carlsbad, [16]

- [17] CA.

- [18] Khor, C.Y., Abdullah, M.Z. and Ani, F.C., 2012. Underfill process for two parallel plates and flip chip packaging. International communications in heat and mass transfer, 39(8: 1205-1212. https://doi.org/10.1016/j.icheatmasstransfer.2012.07.006 Khor, C.Y., Abdullah, M.Z. and Abdul Mujeebu, M., 2012. Influence of

- [19] gap height in flip chip underfill process with non-Newtonian flow between two parallel plates, Journal of Electronic Packaging. 134(1): 011003 (6 pages) DOI: https://doi.org/10.1115/1.4005914

- Majid, M.F.M.A., Khor, C.Y., Abdullah, M.K., Abdullah, M.Z., Rahiman, W.Y., Jappar, A. and Aris, M.S., 2012, November. Three Dimensional Numerical Prediction of Epoxy flow during the underfill process in flip chip packaging. In 2012 35th IEEE/CPMT International Electronics [20] Manufacturing Technology Conferent https://doi.org/10.1109/IEMT.2012.6521810 Conference (IEMT). 1-6.